Product Summary

The MT46H32M16LFCK-6 IT is a 512mb mobile DDR. This document describes critical product differences associated with the 512Mb Mobile (LP) DDR SDRAM product as it transitions from 95nm process technology to 78nm process technology. Micron makes every effort to ensure that new replacement products have full functional compatibility with previous products. The MT46H32M16LFCK-6 IT is accomplished through design, ATE characterization, and target system validation when possible. It is therefore unlikely that a system that has been designed with a Micron LP DDR SDRAM product will have any problems with a Micron replacement product. Micron does recommend, however, that the MT46H32M16LFCK-6 IT design be fully evaluated with the final version of the new product prior to conversion.

Parametrics

MT46H32M16LFCK-6 IT absolute maximum ratings: (1)VDD supply voltage relative to VSS VDD: –1.0, 2.3V; (2)VDDQ supply voltage relative to VSSQ VDDQ: –0.5, 2.3V; (3)VDDL supply voltage relative to VSSL VDDL: –0.5, 2.3V; (4)Voltage on any ball relative to VSS VIN, VOUT: –0.5, 2.3V; (5)Input leakage current; any input 0V ≤ VIN ≤ VDD; all other balls not under test = 0V II: –5, 5μA; (6)Output leakage current; 0V ≤ VOUT ≤ VDDQ; DQ and ODT disabled IOZ: –5, 5μA; (7)VREF leakage current; VREF = valid VREF level IVREF: –2, 2μA.

Features

MT46H32M16LFCK-6 IT features: (1)VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V; (2)JEDEC-standard 1.8V I/O (SSTL_18-compatible); (3)Differential data strobe (DQS, DQS#)option; (4)4n-bit prefetch architecture; (5)Duplicate output strobe (RDQS)option for x8; (6)DLL to align DQ and DQS transitions with CK; (7)4 internal banks for concurrent operation; (8)Programmable CAS latency (CL); (9)Posted CAS additive latency (AL); (10)WRITE latency = READ latency - 1 tCK; (11)Selectable burst lengths: 4 or 8; (12)Adjustable data-output drive strength; (13)64ms, 8192-cycle refresh; (14)On-die termination (ODT); (15)Industrial temperature (IT)option; (16)Automotive temperature (AT)option; (17)RoHS-compliant; (18)Supports JEDEC clock jitter specification.

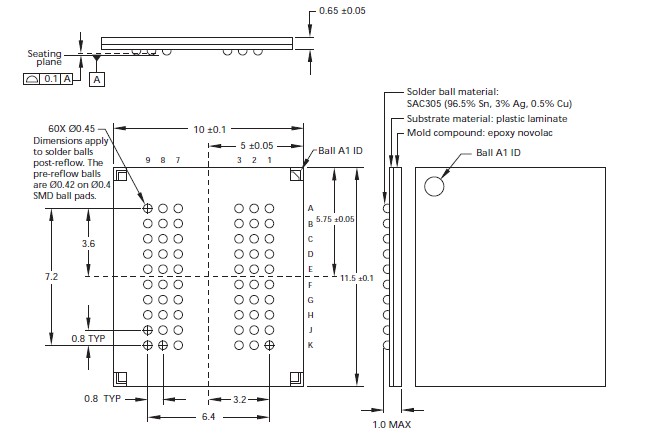

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MT46H32M16LFCK-6 IT TR |

|

IC DDR SDRAM 512MBIT 60VFBGA |

Data Sheet |

Negotiable |

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

MT46H128M16LFCK-5 IT:A |

|

IC DDR SDRAM 2GB 200MHZ 60VFBGA |

Data Sheet |

|

|

||||||

|

MT46H128M16LFCK-6 IT:A |

|

IC DDR SDRAM 2GB 200MHZ 60VFBGA |

Data Sheet |

|

|

||||||

|

MT46H128M32L2KQ-5 IT:A |

|

MOBILE LPDDR 1.8V 200MHZ 5NS |

Data Sheet |

|

|

||||||

|

MT46H128M32L2MC-5 IT:A |

|

IC DDR SDRAM 2GB 200MHZ 240WFBGA |

Data Sheet |

|

|

||||||

|

MT46H128M32L2MC-6 IT:A |

|

IC DDR SDRAM 2GB 200MHZ 240WFBGA |

Data Sheet |

|

|

||||||

|

MT46H16M16LF 4 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

(China (Mainland))

(China (Mainland))